Un groupe de huit acteurs majeurs de l’informatique et de l’Internet s’est formé autour d’IBM et des microprocesseurs Power. Il défie Intel.

AMD, Dell EMC, Google, HPE, IBM, Mellanox Technologies, Micron, NVIDIA et Xilinx lance le consortium OpenCAPI et publie une nouvelle spécification éponyme qui devrait permettre de développer des serveurs dont le niveau de performance pourrait être multiplié jusqu’à un facteur 10. Les premiers produits fondés sur cette interface devraient être disponibles à partir de la deuxième moitié 2017. Dans ce groupe, on trouve les leaders HPE et Dell du marché des serveurs x86. Certains des membres sont motivés pour pousser une plus grande diversité technologique. Car si Intel est de loin le numéro des microprocesseurs x86, il est aussi à l’origine de nombreuses technologies de connexion entre les processeurs et les éléments périphériques.

IBM n’a pas grand grand-chose à perdre. Selon IDC, les revenus provenant des serveurs IBM basés sur le microprocesseur Power a baissé de 34 % au deuxième trimestre 2016 à 1,3 milliard de dollars alors que, sur le même période, ceux des serveurs x86 ont augmenté de 7 % pour atteindre 11,6 milliards de dollars. Après avoir fait cavalier seul pendant de nombreuses années, IBM a ouvert son architecture Power en 2103 en lançant l’alliance OpenPower avec Google, IBM, NVIDIA, Mellanox et Tyan. Cette alliance vise à développer des technologies dans le domaine des serveurs, des réseaux, des cartes graphiques et du stockage afin d’offrir plus de choix et de flexibilité aux développeurs des data centers de prochaine génération, de très grande taille et optimisés pour le cloud. Avec OpenCAPI, IBM pousse cette approche encore plus loin. La spécification OpenCAPI est ouverte gratuitement à tous.

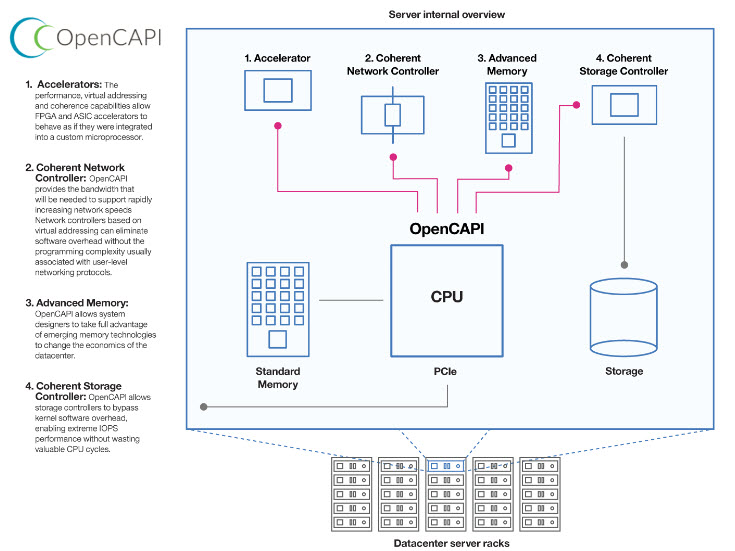

La nouvelle norme, baptisée OpenCAPI et qui vient d’être publiée par le consortium OpenCAPI nouvellement formé, permettra de développer de nouvelles technologies : mémoire avancée, des accélérateurs, des réseaux et de stockage – d’intégrer plus étroitement leurs fonctions au sein des serveurs.

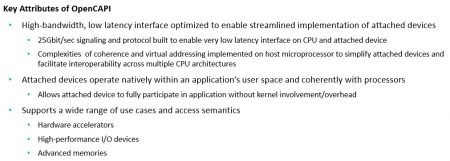

Pour les membres de ce consortium, cette approche centrée sur les données pour la conception de serveur met la puissance de calcul de plus près les données et élimine les inefficacités dans les architectures de systèmes traditionnels. OpenCAPI établit une nouvelle norme, fournissant une bande passante élevée et la spécification de conception d’interface ouverte à faible latence conçue pour minimiser la complexité de la conception de l’accélérateur de haute performance. Supportant un débit de 25Gbit/s, OpenCAPI surpasse la spécification PCIe actuelle qui offre un taux de transfert de données maximum de 16Gbit/s.

PCI Express a-t-il atteint ses limites ?

Le PCI Express, abrégé PCI-E ou PCIe (anciennement 3GIO, 3rd Generation Input/Output) est un standard développé par Intel et introduit en 2004. Il spécifie un bus local série (« bus PCI express ») et un connecteur qui sert à connecter des cartes d’extension sur la carte mère d’un ordinateur. Il est destiné à remplacer tous les connecteurs d’extension d’un PC, dont le PCI et l’AGP. La spécification 4.0 est prévue pour 2016 mais probablement plutôt en 2017. Un intérêt notable du bus PCIe est que deux cartes PCIe peuvent dialoguer entre elles sans passer par le processeur.

OpenCAPI répond à des besoins de certains secteurs comme la finance, les services Internet, le commerce de détail, l’hôtellerie, médicale et l’industrie automobile qui mettent en œuvre des applications manipulant des volumes de données très importants.

Après une longue période de collaboration menant à la libération de la spécification OpenCAPI, plusieurs sociétés de technologie ont des plans pour introduire et déployer OpenCAPI produits compatibles, parmi lesquels on peut mentionner :

– IBM prévoit d’introduire des serveurs basés sur POWER9 qui exploitent la spécification OpenCAPI dans la seconde moitié de 2017. En outre, IBM permettra aux membres de la Fondation OpenPower d’introduire OpenCAPI produits activés dans la seconde moitié 2017.

– Des nouveaux serveurs de Google et Rackspace en cours de développement, le nom de code Zaius et annoncé lors du Sommet OpenPower à San Jose, mettra à profit la technologie POWER9 et des plans pour fournir l’interface OpenCAPI dans sa conception processeur.

– Mellanox prévoit de permettre aux nouvelles capacités de spécification dans ses futurs produits.

– Xilinx prévoit d’introduire des circuits programmables (FPGA) basés sur la norme OpenCAPI.

Le consortium OpenCAPI est la troisième organisation qui vient d’être créé dans le domaine des normes ouvertes pour le data center avec CCIX (Cache Coherent Interconnect for Accelerators) et Gen-Z.

puis

puis