Face aux difficultés de plus en plus grandes de poursuivre la Loi de Moore et en attendant de nouvelles idées comme les ordinateurs quantiques, les spécialistes proposent de creuser l’approche Software-in-Silicon pour continue à améliorer les performances.

A la récente conférence ISSCC (IEEE international Solid-State Circuits Conference) qui s’est tenue en février dernier à San Francisco, Bill Holt, Executive Vice President d’Intel a confirmé qu’au-delà des processus de lithographie, les ingénieurs seraient confrontés aux lois de la physique et ne pourraient plus aller beaucoup plus loin.

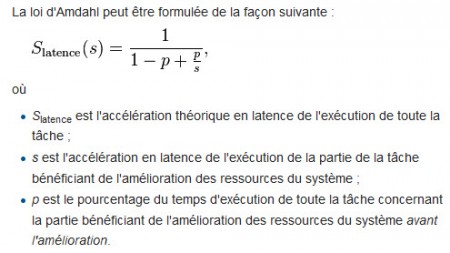

Du côté de la vitesse d’horloge des processeurs, l’évolution a été tout aussi spectaculaire pour connaître un plafond de verre au milieu des années 2000. En 2002, le Pentium 4 avait atteint une fréquence de 3 GHz alors que, un peu plus d’une décennie plus tard, la dernière génération des Xeon culmine à 3,6 GHz. Avec ses processeurs Power, IBM a réalisé 4 GHz et il arrive à 5,2 GHz pour ses processeurs utilisés dans ses mainframes. Les fabricants de microprocesseurs ont alors multiplié le nombre de cœurs sur un même socket. C’est là une approche qui est proche de celle du parallélisme et qui, elle-aussi, limitée par la Loi d’Amdahl[1] (voir ci-dessous).

Le résultat concret est que 16 à 32 cœurs est le nombre maximum de cœurs qui peuvent être utilisés efficacement pour la majorité des applications. Aller au-delà ne sert pas à grand-chose. Parmi les voies d’amélioration des performances, l’utilisation des disques SSD ainsi que l’utilisation des format PCIe et du protocole NVMe en remplaçant du traditionnel SCSI réduit significativement le temps de latence et garantit que ce temps est prédictible. Sur les disques traditionnels, il est fonction de la position des données sur les plateaux et du temps nécessaires pour y accéder.

_________

[1] La loi d’Amdahl est souvent utilisée en calcul parallèle pour prédire l’accélération théorique lors de l’utilisation de plusieurs processeurs. Par exemple, si un programme a besoin de 20 heures d’exécution sur un processeur uni-cœur et qu’une partie du programme qui requiert une heure d’exécution ne peut pas être parallélisée, même si les 19 heures (p = 95 %) d’exécution restantes peuvent être parallélisées, quel que soit le nombre de processeurs utilisés pour l’exécution parallèle du programme, le temps d’exécution minimal ne pourra passer sous cette heure critique. Ainsi, l’accélération théorique est limitée au plus à 20 (1/(1 − p) = 20). On en déduit deux règles. Premièrement, lors de l’écriture d’un programme parallèle il faut limiter autant que possible la partie sérielle. Deuxièmement, un ordinateur parallèle doit être un excellent ordinateur sériel pour traiter le plus rapidement possible la partie sérielle.

puis

puis