C’est à la conférence HotChips, qui s’est tenue à l’université de Stanford que Cerebras a dévoilé Wafer Scale Engine (WSE), le processeur le plus grand jamais développé.

C’est à la même conférence qu’Intel avait présenté NNP-I, sa puce spécialisée pour l’IA (Intel dévoile une puce spécialisée pour l’IA). Destinée au calcul haute performance, cette puce NNP-I (Neural Network Processor Inference) destinée au deep learning dans les grands datacenters a été développée sous le nom de code Spring Hill à Haïfa en s’appuyant notamment sur les travaux de Nervana Systems, une start-up israélienne acquise en 2016. Le développement de puces spécialisées pour l’IA, la Machine Learning ou le Deep Learning est clairement une tendance majeure de l’industrie.

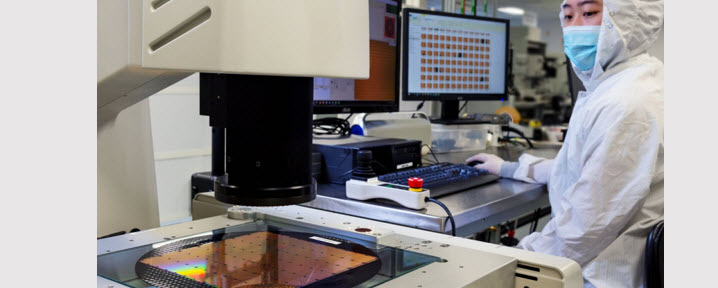

Le WSE est présentée comme la plus grande puce commerciale jamais fabriquée, conçue pour résoudre le problème du Deep Learning. Le WSE est constitué de 1,2 trillion de transistors, intégrés sur une seule puce de 215 mm x 215 mm avec 400 000 cœurs optimisés pour l’IA, reliés par une interconnexion à 100 Pbit / s. Les cœurs sont alimentés par 18 Go de mémoire ultra-rapide sur puce, avec une bande passante mémoire de 9 PB / s.

« L’apprentissage en profondeur (Deep Learning) est un des plus importants défis de l’informatique et la plus exigeante en puissance de calcul, considère Sean Lie, architecte de la puce et co-fondateur de Cerebras. C’est pourquoi nous avons besoin de processeurs spécialisé ». Il n’y a pas encore de puce de production et si Sean Lie a déclaré que les premiers clients exécutaient des charges de travail sur des processeurs de pré-production, il n’a pas précisé quand le produit serait commercialement disponible.

Un processeur mesure 215 millimètres de côté, soit une surface totale est environ 56 fois plus grande que le processeur graphique GV100 de Nvidia, le standard de référence actuel en matière de formation de réseaux de neurones. En conséquence, la puce Cerebras possède 78 fois plus de cœurs que le GV100 (même si tous les cœurs ne se valent pas).

La startup Cerebras rejoint les nombreuses entreprises qui conçoivent des processeurs personnalisés pour l’apprentissage automatique. Mais Cerebras est le premier et le seul à utiliser l’intégration à l’échelle du Wafer.

L’un des gros avantages de l’intégration à l’échelle des tranches est le potentiel d’économie réalisé en termes de fabrication d’intégration, qui peut représenter jusqu’à la moitié du coût d’une puce. L’autre grand avantage est le potentiel d’amélioration des performances, en particulier dans les cas où des niveaux élevés d’intensité de calcul sont souhaités, ce qui était la principale motivation des concepteurs Cerebras.

À ce stade, la plupart des applications de Deep Learning sont accélérées sur les GPU, l’accélérateur Tesla V100 de Nvidia étant le processeur le plus performant.

Là où Cerebras se distingue d’Intel et de Nvidia, le deep learning nécessite un niveau d’intégration beaucoup plus élevé que celui que les puces conventionnelles peuvent offrir, et le moyen d’y parvenir passe par une intégration à l’échelle des Wafer. En particulier, en mettant des centaines de milliers de cœurs, plusieurs Go de mémoire SRAM (non DRAM) et une matrice haute vitesse sur la puce, Cerebras prétend pouvoir obtenir de meilleures performances. L’intégration au niveau de la puce facilite également la conception personnalisée des processeurs, de la mémoire et du réseau.

La plupart des réseaux de neurones utilisent la mémoire locale pour les pondérations, l’activation et l’arithmétique tenseur, avec peu de réutilisation des données. Cela rend la mise en cache ou d’autres types de hiérarchies de mémoire moins nécessaires. Ici, les 18 Go de mémoire, sous forme de mémoire SRAM, sont répartis sur les cœurs.

Cerebras a encore du travail à faire sur le plan logiciel. Mais cet aspect a été pris en compte en même temps que le développement de la puce elle-même. le logiciel système est capable d’extraire le réseau neuronal de frameworks telq que TensorFlow et PyTorch et de les mapper sur la structure de calcul Cerebras. La taille des couches réseau détermine la quantité de ressources de calcul fournies.

L’alimentation et le refroidissement sont l’un des autres problèmes importants posés par ces grandes plaquettes. Les contraintes thermiques, en particulier, posent un problème car le silicium se dilate à des vitesses différentes de celles du substrat du circuit imprimé lorsqu’il est chauffé. Cela ferait craquer la puce si elle devenait trop chaude. Pour résoudre ce problème, Cerebras a utilisé une couche de connecteur personnalisée entre la carte de circuit imprimé et la plaquette, conçue pour absorber la variation de température. De plus, une plaque froide refroidie par eau repose sur le silicium pour maintenir la température de fonctionnement appropriée. La plaquette est alimentée en énergie par plusieurs fils allant de la carte de circuit imprimé au connecteur en passant par le silicium.

puis

puis