À l’occasion de la conférence Hot Chips 2024, IBM a levé le voile sur les processeurs qui équiperont sa prochaine génération de mainframes Z.

Le Z16 est sorti en 2022, trois ans à peine après le Z15. Le cycle de renouvellement des mainframes dans le catalogue IBM s’est accéléré. Et le constructeur prépare déjà le futur Z17 ! Une façon de montrer que les mastodontes de l’informatique sont toujours aussi vivants.

Et même s’il est encore trop tôt pour dévoiler le Z17, IBM a profité de la conférence Hot Chips 2024 pour évoquer les futurs composants et accélérateurs qui animeront son prochain mainframe.

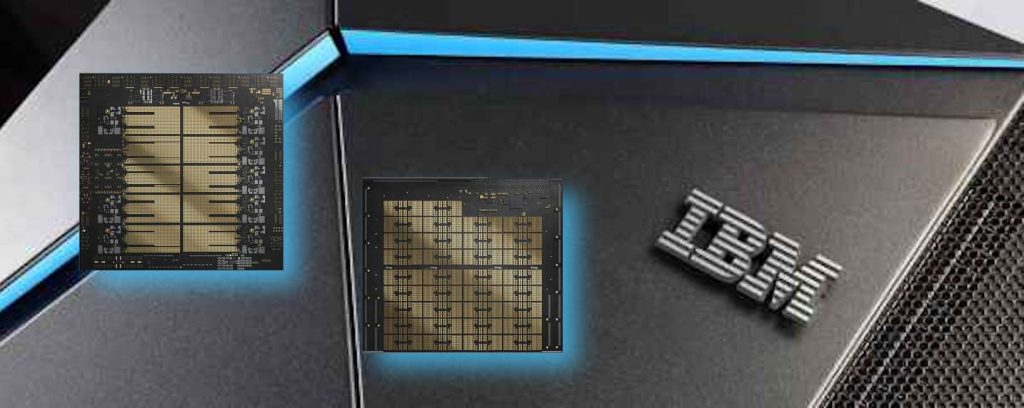

Deux nouvelles puces ont ainsi été présentées.

Un nouveau CPU « Telum II »

La première est le nouveau CPU « IBM Telum II » qui succède au « Telum » des actuels Z16. Au menu, plus de fréquence, plus de mémoire, plus de cache et plus d’IA mais – et c’est assez surprenant – pas plus de cœurs !

Le Tellum II est un processeur qui dérive des anciens Power PC mais incorpore des accélérations pour l’IA ainsi qu’un DPU (Digital Processing Unit). Il comporte huit cœurs haute performance fonctionnant à 5,5 GHz, avec 36 Mo de cache L2 par cœur et une augmentation de 40 % de la capacité de cache sur puce pour un total de 360 Mo. Le cache virtuel de niveau 4 de 2,88 Go par tiroir offre une augmentation de 40 % par rapport à la génération précédente.

Présenté comme 4 fois plus performant que celui du Telum, l’accélérateur d’IA (NPU) intégré accélère les inférences et promet haut débit et faible latence sur l’exécution des IA pendant les transactions, par exemple en améliorant la détection des fraudes lors des transactions financières. Par ailleurs, les enrichissements apportés à cet accélérateur IA intégré prennent en compte les besoins des LLM modernes.

Une toute nouvelle unité de traitement des données (DPU) fait également son apparition sur la puce Telum II. Elle est conçue pour accélérer les protocoles réseau complexes et améliorer le traitement des données avec une densité I/O accrue de 50 %. L’introduction de ce DPU devrait contribuer à améliorer l’efficacité globale et l’évolutivité des futurs IBM Z tout en les rendant plus adaptés aux charges de travail IA à grande échelle.

Un accélérateur d’apprentissage IA

L’accélérateur IBM Spyre est l’autre grande nouveauté. Conçue spécifiquement pour compléter les fonctionnalités du Telum II et fonctionner avec lui, cette nouvelle puce sera très probablement optionnelle. Elle est conçue pour accélérer les phases d’apprentissage des IA (là où le NPU interne du Telum II accélère les phases d’inférence).

Chaque puce accélératrice Spyre est attachée au système via une carte PCIe de 75 watts et est basée sur une technologie développée en collaboration avec IBM Research. Chaque carte dispose jusqu’à 1 To de mémoire et est conçue pour travailler en tandem avec les 7 autres cartes accélératrices que peut embarquer un tiroir standard IBM Z.

Chaque puce Spyre dispose de 32 cœurs de calcul prenant en charge les types de données int4, int8, fp8 et fp16 pour les applications d’IA à faible latence et à haut débit.

« Le processeur Telum II et l’accélérateur Spyre sont conçus pour fournir des solutions informatiques d’entreprise haute performance, sécurisées et plus économes en énergie » explique Tina Tarquinio, VP, Gestion des produits, IBM Z et LinuxONE avant de confirmer qu’ « après des années de développement, ces innovations seront introduites dans notre prochaine génération de plateforme IBM Z afin que les clients puissent tirer parti des LLM et de l’IA générative à grande échelle. »

puis

puis