A l’occasion de la conférence Hot Chips, IBM présente son Power8 tandis que la HSA Foundation lève le voile de la nouvelle génération de puces.

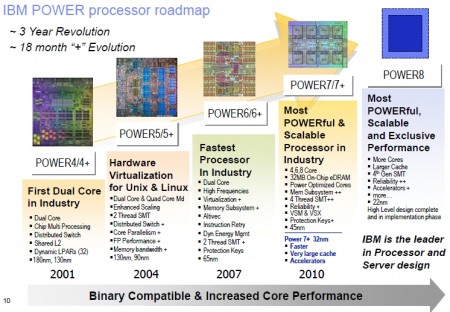

C’est en 2014 qu’IBM devrait lancer la nouvelle génération de son microprocesseur Power8 pour laquelle il fait une présentation intitulée « Next Generation Power Microprocesseur » à la conférence Hot Chips qui se tient jusqu’à demain au Stanford Memorial Auditorium. IBM reste donc dans la course à la performance et entend garantir la destinée de ses serveurs maison. La prochaine étape est donc l’annonce du Power8 avec lequel IBM devrait passer directement du 32nm utilisé pour le Power7 et 7+ à la technologie 22nm. Un saut comparable à celui effectué par Intel avec ses processeurs Xeon.

Cette évolution est le résultat d’une amélioration continue depuis l’introduction du premier microprocesseur d’Intel il y a un peu plus de 40 ans qui utilisaient des procédés de 10 micromètres.

Ce surcroit de miniaturisation devrait permettre à IBM de déposer plus de cœurs dans le même espace, de disposer de caches plus importantes. Le Power8 devrait aussi utiliser la quatrième génération de technologies multihread permettant de supporter plus de threads par cœurs, 6 ou 8 contre 4 pour les microprocesseurs actuels. Ci-dessous la Roadmap du Power8 publiée par le magazine en ligne Spécialisé IT Jungle.

Parallèlement, IBM a annoncé début août la création de l’OpenPower Consortium, une alliance au travers de laquelle IBM entend ouvrir la propriété intellectuelle autour de l’architecture Power – spécifications des processeurs, du firmware, du logiciel – et visant à adopter un mode de développement collaboratif. Toutefois, l’architecture Power est toujours sous le contrôle de l’organisation Power.org.

L’OpenPower Alliance ne réunit pour l’instant que quatre autres membres : Google, Nvidia, Mellanox et Tyan. La démarche prônée par IBM est similaire à celle de l’ARM Holdings autour des processeurs ARM qui s’est imposée dans les marchés des téléphones portables et des tablettes mais aussi sur les marchés de l’embarqué. L’objectif pour IBM est sans doute de recréer une dynamique autour de l’architecture Power et d’assurer le futur de ses propres serveurs mais aussi de tous les composants qui sont conçus autour. En revanche, la stratégie pour Google est mois nette. Le géant de l’Internet veut peut être maintenir la pression dans la course à l’innovation sur Intel et, dans une moindre mesure, sur AMD. Le géant de l’Internet bénéficie déjà de microprocesseurs personnalisés fabriqués par Intel pour construire ses propres serveurs et systèmes de stockage.

Clairement, Power a perdu du terrain face à ses concurrents. Il y a une dizaine d’années encore, Apple utilisait encore les microprocesseurs PowerPC pour ses Mac avant de passer à puces Intel ainsi que les trois grands fabricants de consoles de jeux Sony, Nintendo et Microsoft.

La troisième vague

La 25e édition de la conférence Hot Chips est également l’occasion d’une présentation de la HSA Foundation (Heterogeneous Foundation Architecture), un consortium de fournisseurs de SoC (System on a Chip), de concepteurs, d’éditeurs de logiciels et d’entreprises telles qu’ARM, AMD ou Samsung. L’heterogeneous computing est présenté comme la troisième vague de l’informatique (où de l’électronique) après celle des microprocesseurs mono cœurs, puis multi cœurs. A chaque vague, les premiers modèles de programmation ont été relativement simples pour ensuite s’améliorer et tirer le meilleur parti de l’architecture. Au début des processeurs monocœurs, les développeurs programmaient en assembleur avant d’utiliser ensuite des langages plus sophistiques tels les langages structurés, les langages objets…

Un des objectifs poursuivis avec l’architecture est de placer sur un même niveau les processeurs centraux et les processeurs graphiques et de leur permettre de partager des ressources communes telles que les mémoires partagées. A terme, d’autres processeurs spécialisés tels que les DSP, les DMA ou les accélérateurs de mémoire d’être intégrés avec le même niveau de fonctionnement. Avec, sur le plan logiciel, la possibilité d’utiliser des langages de programmation tels que Java ou C++ sans limitation liée à l’architecture matérielle.

puis

puis